前 言

本文为PS + PL端异构多核案例开发的指引文档,主要对PS + PL端开发案例进行简要介绍。

开发环境

Windows开发环境:Windows10 64bit

开发工具:TD_5.9.1_DR1_2025.1_NL、FD_2025.1_SP1

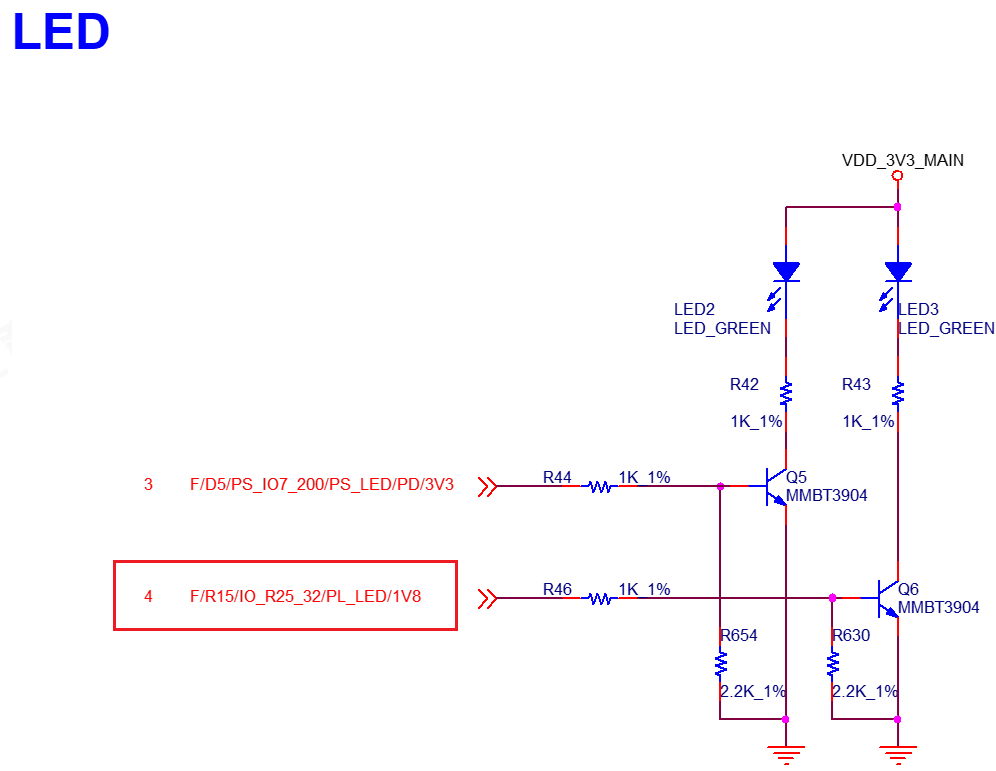

术语表

为便于阅读,下表对文档出现的关键术语进行解释;对于广泛认同释义的术语,在此不做注释。

注意事项

(1)请先按照《开发环境搭建》文档安装TD、FD等软件以及进行JTAG驱动安装,使用下载器(厂家:安路科技,型号:AL-LINK-FT-V1.0)连接评估板JTAG接口至PC端USB接口。

(2)在进行本文操作前,请先参考《TD-FD工程编译与加载》,熟悉工程编译、镜像加载等方法。

(3)案例于产品资料“4-软件资料

DemoFPGA-demosAll-Programmable-SoC-demos”目录下。案例目录详细说明见下表:

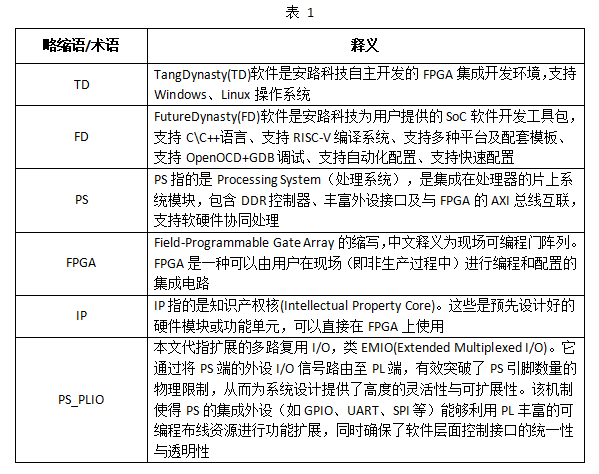

(4)查看案例的Design工程以及约束文件的方法如下,以axi_gpio_led案例进行演示:

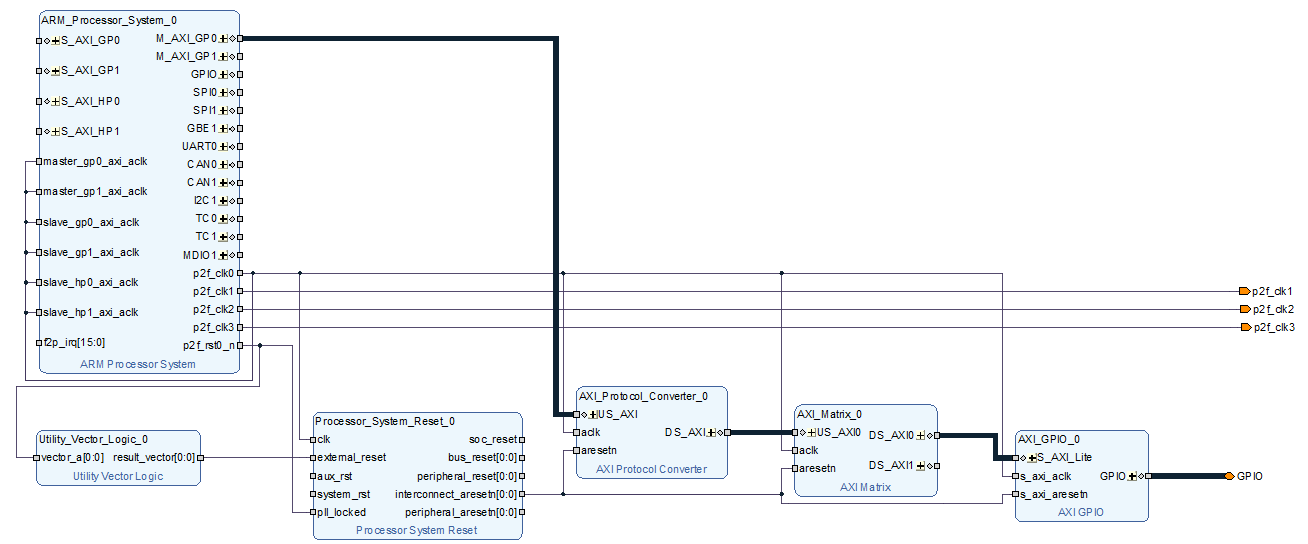

可在TD工程中双击"axi_gpio_led_bd"打开Design Integrator界面。

图 1

图 1

图 2

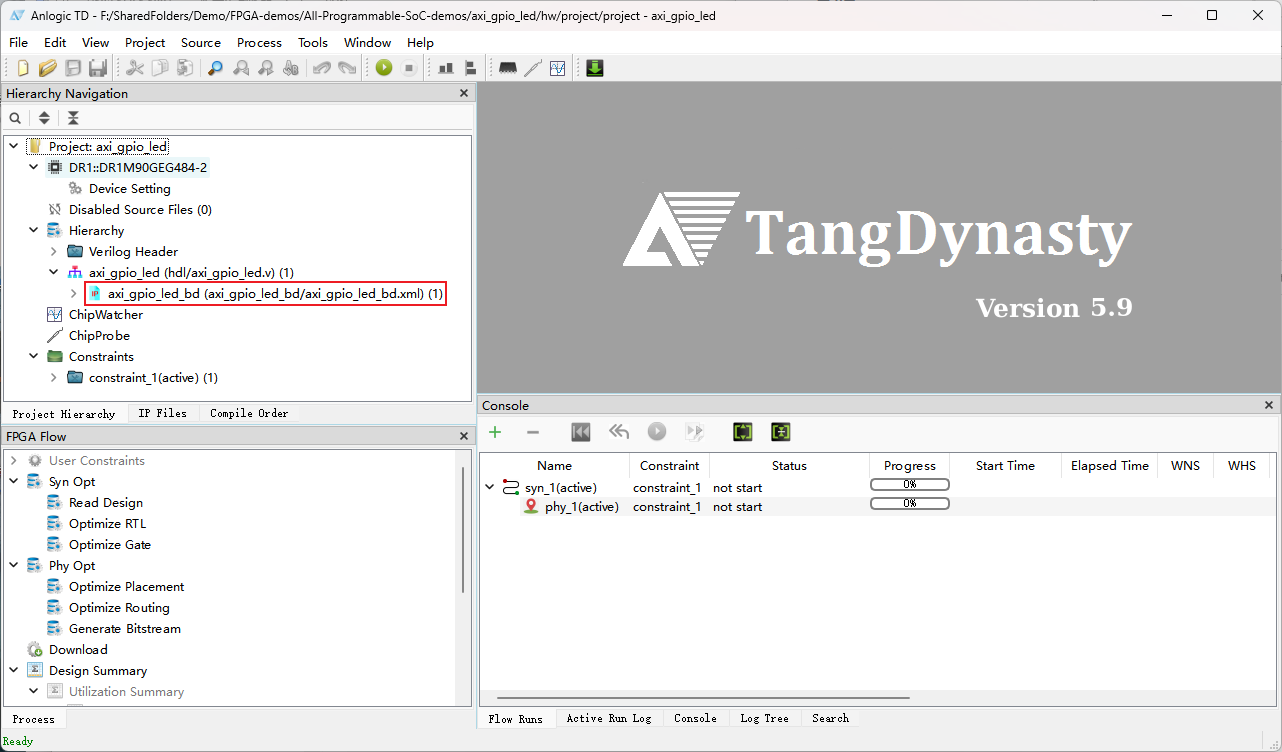

双击"axi_gpio_led_demo.adc"打开.adc约束文件。

图 3

图 3

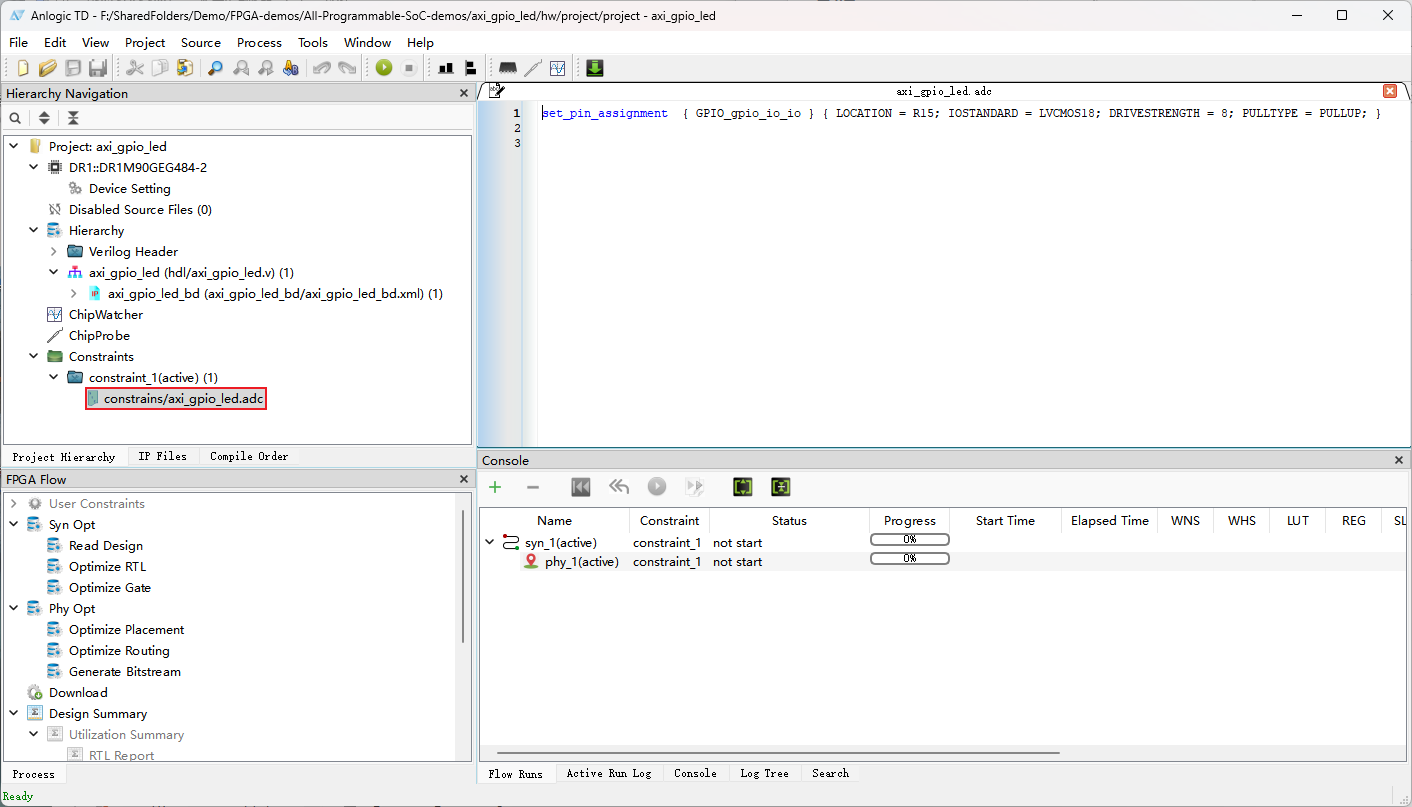

1axi_gpio_led案例

案例功能:PS端通过AXI4-Lite总线发送命令至PL端AXI GPIO IP核,IP核再根据命令控制评估底板PL端LED3的状态。

图 4

图 4

工程管脚约束可查看工程文件"constrains"目录下的.adc约束文件。

1.1 TD工程说明

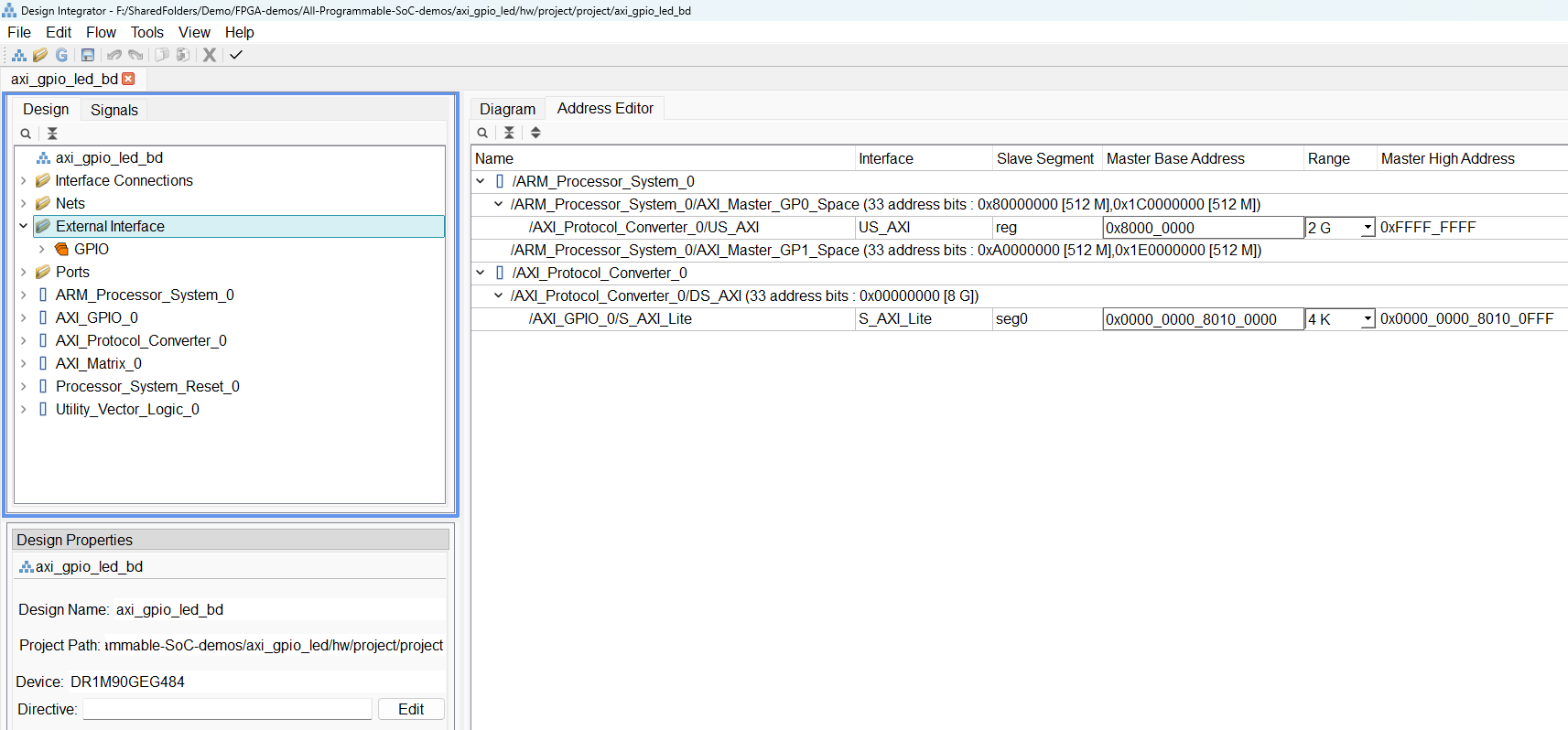

工程在PL端上使用AXI GPIO IP核,ARM Processor System IP核(PS端)通过AXI4-Lite总线可以控制底板的LED亮灭,Design Integrator工程和地址分配如下:

图 5

图 5

图 6

图 6

1.2 IP核简介

IP核开发相关资料可查阅产品资料“6-开发参考资料Anlogic官方参考文档”目录下文档,IP核配置参数如下。

(1)ARM Processor System

ARM Processor System IP核心配置和FSBL工程一致,详细配置可参考位于产品资料“4-软件资料LinuxFSBLfsbl-[版本号]”目录下的FSBL工程。

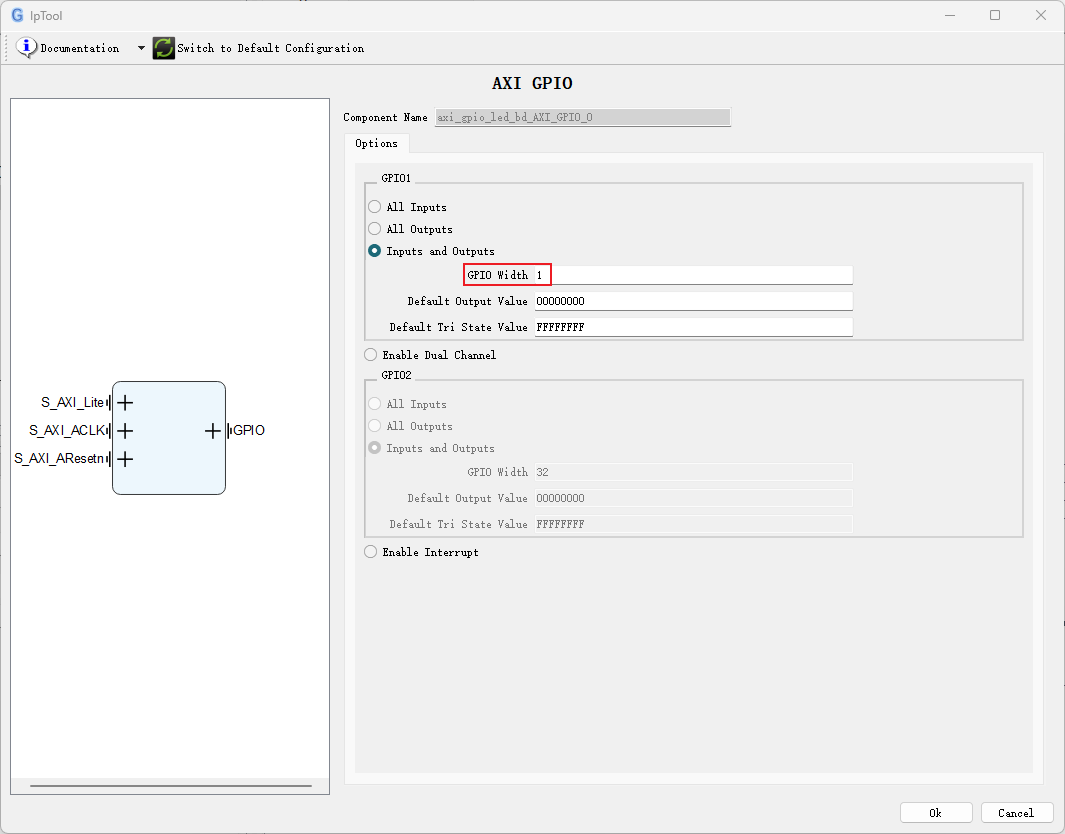

(2)AXI GPIO

图 7

图 7

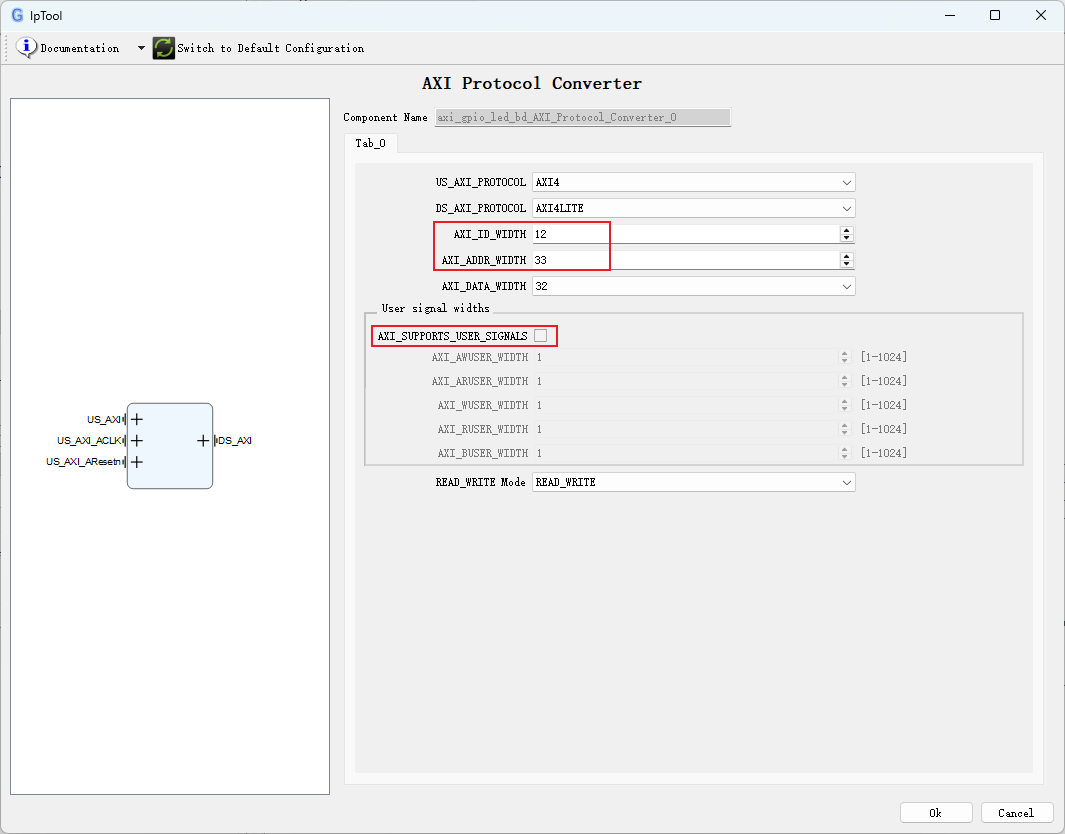

(3)AXIProtocolConverter

图 8

图 8

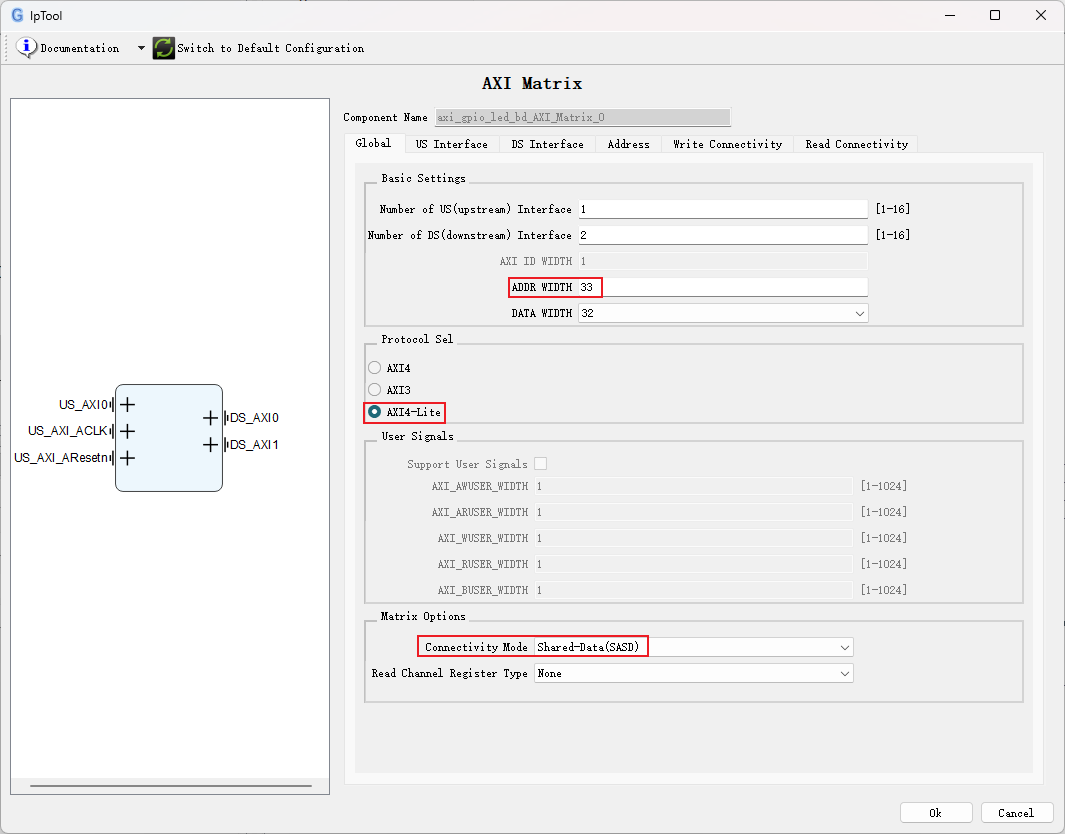

(4)AXIMatrix

图 9

图 9

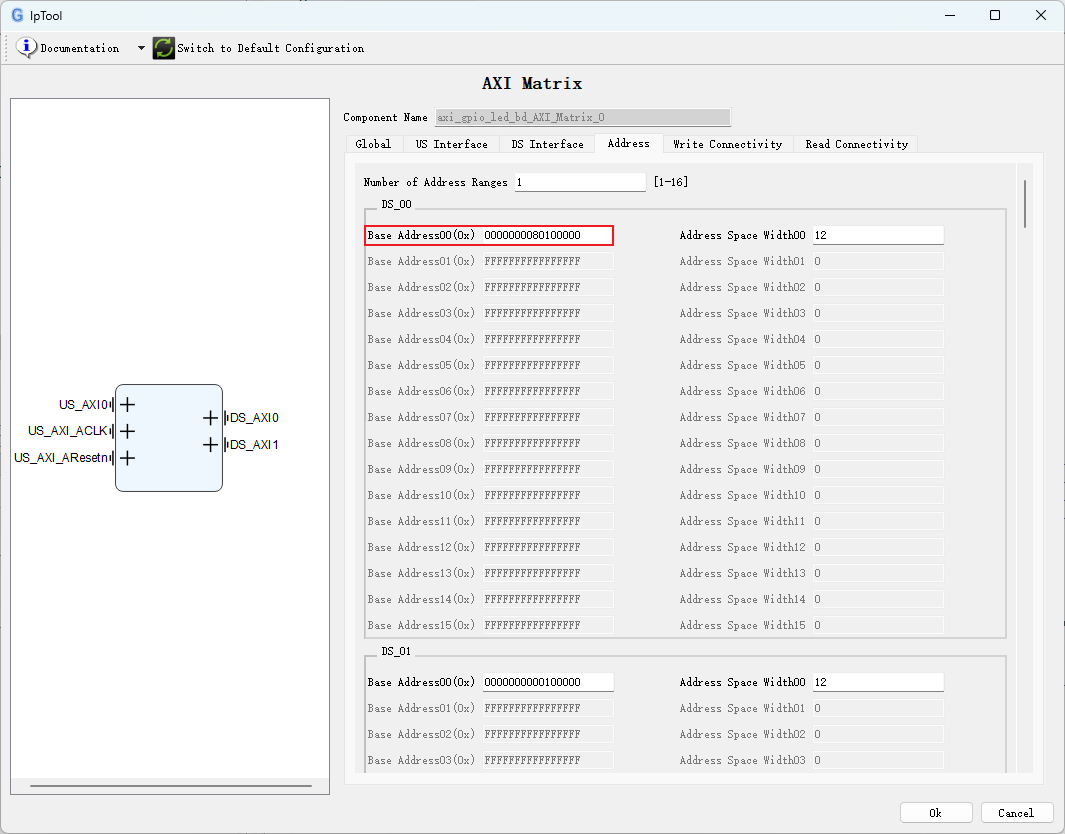

图 10

图 10

1.3 案例测试

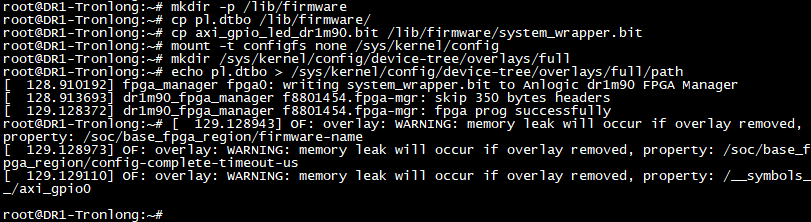

将本案例的动态设备树镜像文件pl.dtbo和PL端.bit镜像文件拷贝至"/lib/firmware/"目录下(若该目录不存在,请新建),并将PL端可执行文件重命名为system_wrapper.bit,然后执行如下命令加载PL端镜像。

Target# mkdir -p /lib/firmware

Target# cp pl.dtbo /lib/firmware/

Target# cp axi_gpio_led_dr1m90.bit /lib/firmware/system_wrapper.bit

Target# mount -t configfs none /sys/kernel/config

Target# mkdir /sys/kernel/config/device-tree/overlays/full //创建full目录,可根据实际情况修改

Target# echo pl.dtbo > /sys/kernel/config/device-tree/overlays/full/path //dtbo文件名称请根据实际情况修改

图 11

图 11

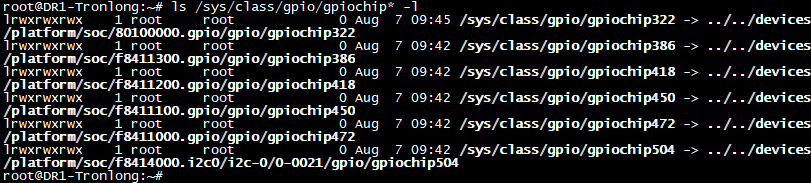

查看"/sys/class/gpio/"目录下生成的gpiochip322节点,地址为0x80100000,与axi_gpio_led案例给AXI GPIO IP分配的地址一致。

Target# ls /sys/class/gpio/gpiochip* -l

图 12

图 12

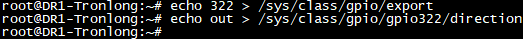

生成gpio322节点,配置gpio322为output。

Target# echo 322 > /sys/class/gpio/export

Target# echo out > /sys/class/gpio/gpio322/direction

图 13

图 13

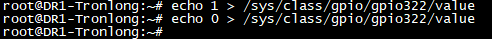

通过gpio322控制评估底板LED3亮灭。

Target# echo 1 > /sys/class/gpio/gpio322/value

Target# echo 0 > /sys/class/gpio/gpio322/value

图 14

图 14

审核编辑 黄宇